Python-CUDA-CuDNN-Pytorch-Jupyter配置合集

Python CUDA CuDNN Pytorch Jupyter配置合集本文主要内容为使用 uv 搭建隔离的 Python 环境,设置VSCode Jupyter 相关配置,安装匹配显卡的 CUDA 与 cuDNN,并配置并验证 PyTorch GPU 加速。本文拆分为四个部分:

环境与依赖管理(uv)

VSCode Jupyter 相关配置

CUDA / cuDNN 组件

PyTorch 安装、验证与优化

一:uv 环境与依赖管理1. 了解 uvuv 是用 Rust 编写的超快 Python 包与环境管理工具,集成:

Python 版本安装 (多版本共存)

虚拟环境管理

依赖解析与锁定

pip + pip-tools + virtualenv 的组合替代

项目地址:https://github.com/astral-sh/uv

官方教程:https://uv.doczh.com/

uv(以及 virtualenv、venv 等工具)的核心工作原则:隔离。

uv 管理的 Python:干净的“模板库”当您使用 uv tool install python 安装了多个 Pyth ...

Java多版本环境配置

在 Windows 环境配置多版本 Java无论是为了准备 OO 课程,还是游玩 Minecraft,多版本 Java 的需求都不可避免。接下来将介绍在 Windows 环境下配置多版本 Java 环境的教程,帮助读者方便地进行配置和切换。

当然,IDEA 可以读取所有 Java 运行环境,并且通过 GUI 界面简单地切换,并且高版本的 Java 可以设置语言级别以满足 OO 课程对 Java 1.8(JDK8)的要求。本文目的是为了便于管理多版本 Java,以及配置默认的命令行界面 Java 版本。

安装前必读关于 JDK 和 JRE在配置 Java 环境时,常常会遇到 JDK 和 JRE 两个概念。JDK(Java Development Kit)是 Java 的开发工具包,包含了编译器(javac)、调试工具等开发所需的全部内容。JRE(Java Runtime Environment)则是 Java 的运行环境,仅包含运行 Java 程序所需的库和虚拟机(JVM),不包括编译器。

一般来说,如果你只是运行 Java 程序,安装 JRE 即可;但如果需要开发 Java 应用或 ...

BUAA-OS-shell

BUAA OS LAB6-SHELL 大作业报告前言本来一开始准备写swap,但在长达四天的swap奋战后,OS大作业取得了惊人的突破:转战shell

总计增删代码量为 2176 行。

相比于swap里的云里雾里,shell指导书相对清晰有逻辑。

然后,感谢懒鱼提供思路,对于内核态的修改路径帮助很大,虽然解析还是使用课程组的史山。不过能有OO纯正则解决表达式难?

BUAA-OO-unit1 | wrongization

北航2025 OS shell挑战性任务实现指导 | Lazyfish & chilly_river

实现要求参见:任务要求

完整代码参见:代码下载

功能实现不带 .b 后缀指令修改spawn.c

12345678910111213141516171819int spawn(char *prog, char **argv) { // Step 1: Open the file 'prog' (the path of the program). // Return the error if 'open' fail ...

BUAA-OO-unit4

OO Unit4 Summary

回顾一下第四单元完成的任务:利用UML进行正向建模,并完成一个小型的图书馆管理系统

hw13:实现借阅,预约,预约取书,还书等基本流程

hw14: 实现图书室借阅功能,并增加热门书架与普通书架

hw15:引用用户信用积分限制

一、正向建模与开发正向建模与开发是一种软件工程方法,主要用于系统设计和实现过程中,特别是在软件开发和硬件设计领域。这种方法从高层次的需求和概念开始,逐步细化和分解,直到实现细节,整个过程类似于从宏观到微观的构建方式。正向建模与开发强调从抽象到具体、从整体到部分的设计思想,有助于确保系统设计的连贯性和完整性,便于团队成员理解整个系统的工作原理。

OO作业是迭代性任务,一个良好的初期架构对于后期作业的顺利完成是十分重要的,本单元中,课程组的初衷是先绘制UML类图等进行正向建模,并据此进行后续开发。对此,我的做法是首先设计整体框架,抽象出主要类例如书架、借还处、预约处等类,将类聚合到一个总体类图书馆中,对不同操作抽象出一些大的方法,得到一开始的粗略图。在图书馆类中针对不同操作抽象方法,调用不同的组成部分调用其内部具体实现方法,在通 ...

BUAA-OS-LAB6

BUAA OS LAB6 实验报告ThinkingThinking 6.1Q:

示例代码中,父进程操作管道的写端,子进程操作管道的读端。

如果现在想 让父进程作为“读者”,代码应当如何修改?

A:

1234567891011121314151617switch (fork()) { case -1: break; case 0: /* 子进程 - 作为管道的写者 */ close(fildes[0]); /* 关闭不用的读端 */ write(fildes[1], "Hello world\n", 12); /* 向管道中写数据 */ close(fildes[1]); /* 写入结束,关闭写端 */ exit(EXIT_SUCCESS); default: /* 父进程 - 作为管道的写者 */ close(fildes[1]); /* 关闭不用的写端 */ read(fildes[0], buf, 100); /* 从 ...

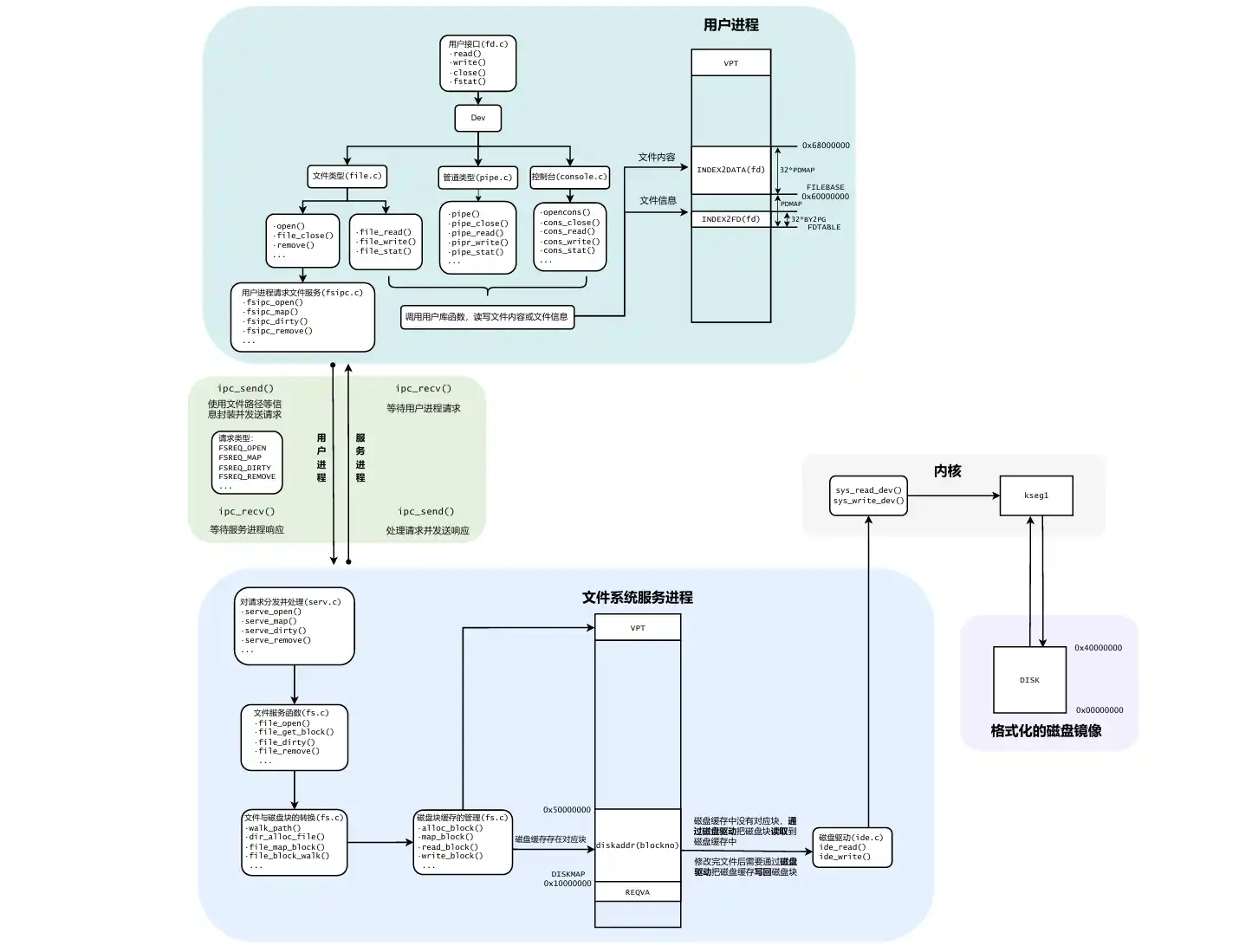

BUAA-OS-LAB5

BUAA OS LAB5 实验报告ThinkingThinking 5.1Q:

如果通过 kseg0 读写设备,那么对于设备的写入会缓存到 Cache 中。这是 一种错误的行为,在实际编写代码的时候这么做会引发不可预知的问题。

请思考:这么做 这会引发什么问题?对于不同种类的设备(如我们提到的串口设备和IDE磁盘)的操作会 有差异吗?可以从缓存的性质和缓存更新的策略来考虑。

A:

当外部设备更新数据时,Cache中旧的数据可能刚刚缓存,那么完成缓存的这一部分无法完成更新,则会发生错误。对于串口设备来说,读写更加频繁,信号密集,在相同的时间内发生错误的可能性远高于IDE磁盘。

Thinking 5.2Q:

查找代码中的相关定义,试回答一个磁盘块中最多能存储多少个文件控制 块?一个目录下最多能有多少个文件?我们的文件系统支持的单个文件最大为多大?

A:

一个文件控制块的大小为256B ,那么一个磁盘块4KB最多存储4KB/256B=16 个文件控制块。

一个目录 = 一个磁盘块全部用来存目录项,又一个目录项32位=4B;则一个目录 4KB ,一个目录中有 4KB/4B=1024 ...

BUAA-OO-unit3

OO Unit3 Summary架构设计梳理:HW9:重点架构设计:第一次作业整体上难度不大,但是需要对jml的实现细节考虑周全,对于一些开销较大的方法需要动态维护以降低时间复杂度,容器尽量使用HashMap等速度较快的。以下列出一些重点方法的实现。

iscircle:

采用朴素bfs加一个visited的map实现去重访问。

queryTripleSum:

采用动态维护,对于添加关系和删除关系,相当于增加或者删除了两人的公共好友数量的三元环。

queryBestAcquaintance:

加入时动态维护最大值,删除时如果删除了最大值重新遍历得到最大值。

getAgeavg/var:

方差和平均数动态维护,注意方差的书写需要考虑整除带来的影响

1return (agesquaresum - 2 * agesum * mean + n * mean * mean) / n;

bug分析和遇到的问题:第一次测试和舍友对拍了许多测试点,公测功能没出现问题,性能卡了一个点,原因是queryTripleSum一开始采用一种将无向图根据度数转换为有向图的方法,复杂度为O($n\sqrt{n}$), ...

BUAA-OS-LAB4

BUAA OS LAB4 实验报告ThinkingThinking 4.1Q:

思考并回答下面的问题:

•内核在保存现场的时候是如何避免破坏通用寄存器的?

•系统陷入内核调用后可以直接从当时的$a0-$a3参数寄存器中得到用户调用msyscall 留下的信息吗?

•我们是怎么做到让sys开头的函数“认为”我们提供了和用户调用msyscall时同样 的参数的?

•内核处理系统调用的过程对Trapframe做了哪些更改?这种修改对应的用户态的变化是什么?

A:

在 SAVE_ALL 中:先 move k0,sp,先把通用寄存器的sp复制到$k0 ;再sw k0,TF_REG29(sp)、sw $2,TF_REG2(sp):保存现场需要使用$v0作为协寄存器到内存的中转寄存器,写到内存时需要sp ,所以在正式保存协寄存器和通用寄存器前先保存这两个寄存器。

可以。从用户函数 syscall_*() 到内核函数 sys_*() 时,$a1−$a3 未改变,$a0在handle_sys() 的时候被修改为内核函数的地址,但在内核函数 sys_*() 仅为占位符,不会被用到。同时,在内 ...

BUAA-OO-unit2

OO Unit2 Summaryhw5:架构设计:

MainClass负责输入,并将对应的Request委派给RequestTable,对应楼座的电梯Elevator通过RequestTable获取请求。这里,我还额外将存储Request的容器封装为一个RequestTable类,这将有利于未来迭代时自由分配指派电梯id。输入线程为主线程,向RequestTable 输入请求,使用线程安全list存储,SafeOutput实现输出安全。

Contorler方法类控制电梯单独行为,获取目标楼层、电梯运动开门等。

生产者:输入线程MainClass托盘:候乘表RequestTable消费者:电梯线程Elevator生产者输入线程获取输入,投放到候乘表RequestTable,消费者电梯线程自己运行,同时扫描RequestTable,找到对应id的乘客后运行。

协作图:

调度:第一次作业不涉及电梯id的分配,只需考虑单电梯的运行策略。

look算法:

当电梯有乘客时,以乘客中目标楼层距离当前楼层最远的请求为主请求确定目标楼层

当电梯没有乘客时,首先按照原方向,寻找距离当前楼层最远的有请求的 ...

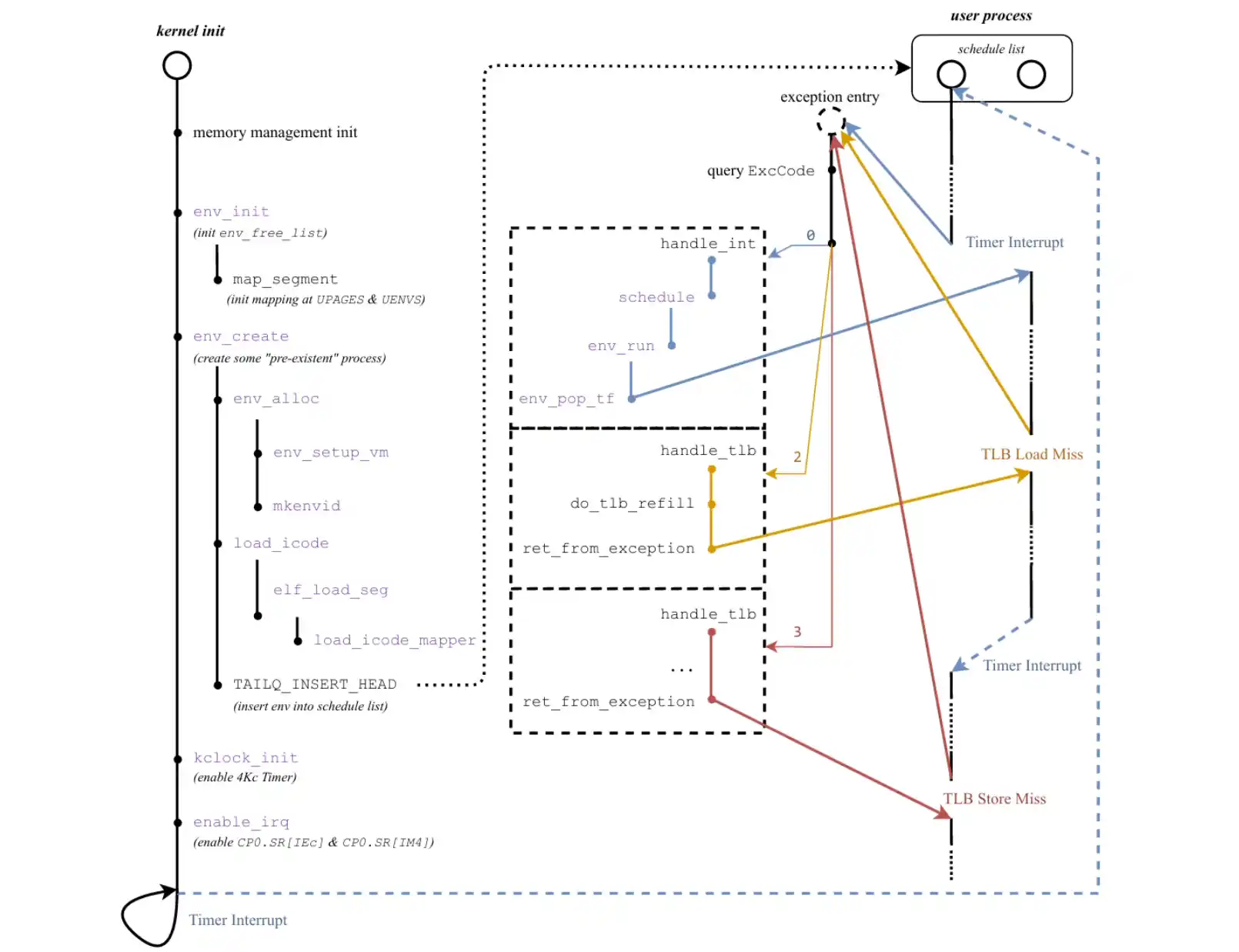

BUAA-OS-LAB3

BUAA OS LAB3 实验报告ThinkingThinking 3.1Q:

请结合MOS中的页目录自映射应用解释代码中e->env_pgdir[PDX(UVPT)] = PADDR(e->env_pgdir) | PTE_V 的含义。

A:

UVPT为整个页表起始虚拟地址,e->env_pgdir[PDX(UVPT)为其对应的一级页表项,即为一个二级页表的基地址,PADDR(e->env_pgdir) | PTE_V为整个页表起始的物理地址,该语句作用为将页目录自身物理地址映射为自身其中的一个一级页表项。

Thinking 3.2Q:

elf_load_seg以函数指针的形式,接受外部自定义的回调函数 map_page。请你找到与之相关的data这一参数在此处的来源,并思考它的作用。没有这个参数可不可以?为什么?

A:

来源:在include/elf.h中可以找到typedef int (*elf_mapper_t)(void *data, u_long va, size_t offset, u_int perm, const void *src,s ...