BUAA-CO-ISE外部运行配置

ISE 外部运行配置

为了避免使用 ISE 自带的界面(其 GUI 界面较为陈旧且运行速度较慢),我们可以选择通过现代化编辑器(如 VS Code)编写 .v 文件,并结合 ISE 的核心工具完成仿真运行。

这种方法不仅提升了开发效率,还能利用 VS Code 的强大功能(如代码高亮、自动补全、版本控制等)优化开发体验。以下是具体的实现步骤和注意事项:

一. 使用 VS Code 编写 Verilog 文件

在项目目录中创建或编辑 .v 文件,确保代码结构清晰、模块划分合理。推荐安装 Verilog HDL 插件以提升编写和调试效率。

vscode插件配置

所有所需下载懒人链接:点击下载

代码格式化

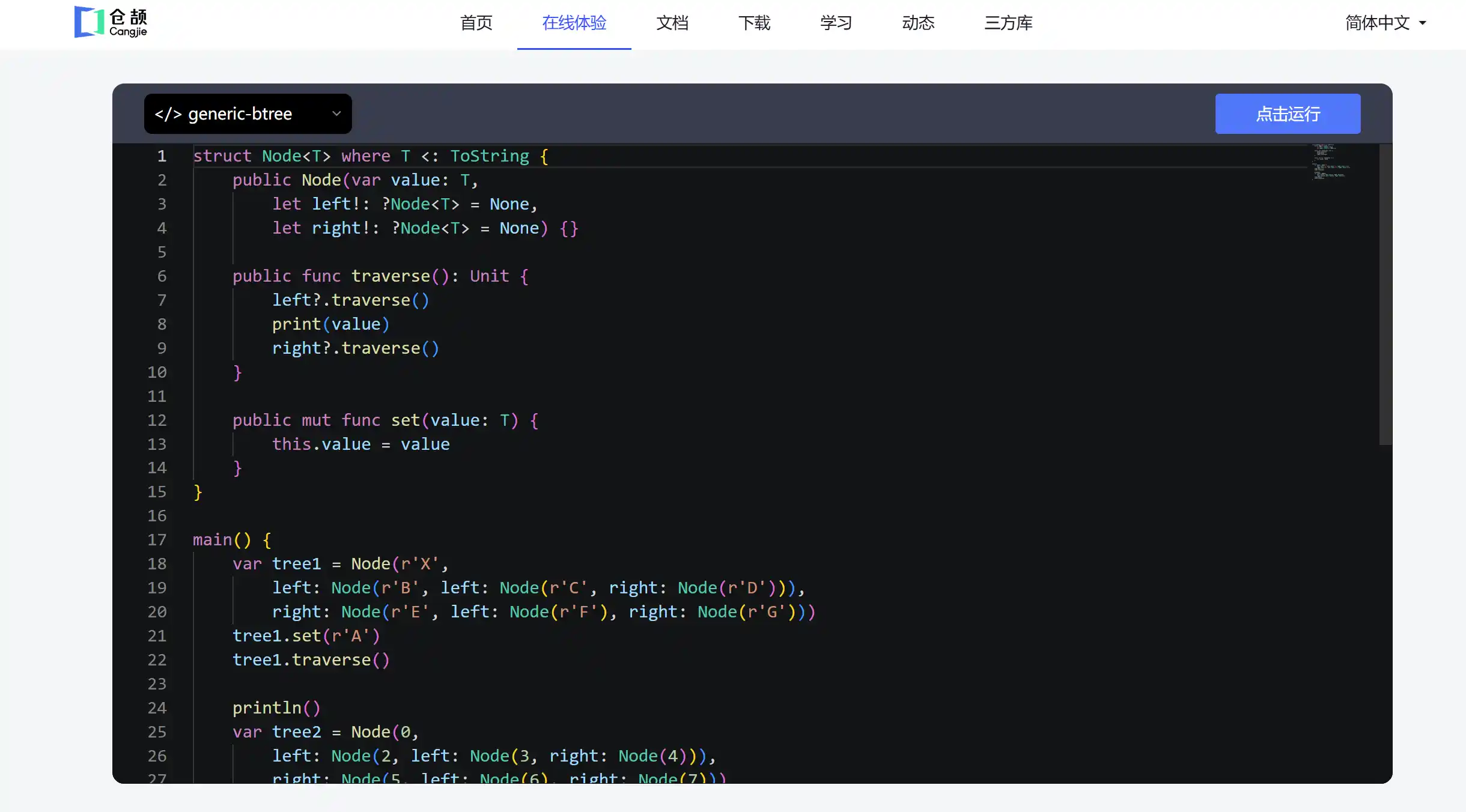

正如上面整体思路中所写,需要在 VSCode 中装一个插件:

然后从 Github 仓库中下载 verible-verilog 工具win64版本:https://github.com/chipsalliance/verible/releases

Windows 直接解压到合适的位置,并复制其中 verible-verilog-format.exe 的地址,填入 VSCode 的设置中:

注意路径不要有空格之类的字符,把引号去掉。

并在设置中(id 为 verilog.formatting.verilogHDL.formatter)将选择 verible-verilog-format 进行格式化。

格式化选项

在这个设置中(id 为 verilog.formatting.veribleVerilogFormatter.arguments)可以配置自己喜欢的格式化参数:

详细的文档可以参考:https://chipsalliance.github.io/verible/verilog_format.html

比较常用的就是一个:--indentation_spaces=4,缩进使用 4 个空格。

此外,通过勾选

editor.formatOnSave设置,可以在保存时自动进行格式化。

语法检查

使用iverilog 进行语法检查,其安装并不困难,然后在设置中将 Linter 选为iverilog (该设置 id 为 verilog.linting.linter )。

然后下载 iverilog 工具:https://bleyer.org/icarus/iverilog-v12-20220611-x64_setup.exe

Windows 直接通过下载的安装程序安装到到合适的位置,并复制其中bin文件夹地址,填入 VSCode的设置中:

下面,是我在使用中遇到的一个问题及解决方法。

iverilog 并不能将识别外部模块,而会显示模块未知。

其解决方案是,在设置中给 iverilog添加一个参数 -i ,不显示模块导入相关报错,并勾选 Run As File Location,这两个设置的 id 分别为 verilog.linting.iverilog.arguments 和 verilog.linting.iverilog.runAtFileLocation。

如果还是不行,在文件开头include所有文件即可。

变量跳转

下载ctags的x64版本:https://github.com/universal-ctags/ctags-win32/releases

将ctags.exe路径填入 VSCode的设置中:

即可实现ctrl+鼠标左键跳转

其他VScode插件

下载verilog highlight插件丰富代码语法高亮颜色。

verilog HDL,等价于iverilog命令加vvp命令,可以在vscode终端运行仿真,由于是单文件运行,引用的模块需要在开头include,而命令行使用通配符编译所有.v文件则反而不需要。

verilog snippet,对一些常用的块结构自动补全

wavetrace, 在vscode中查看vcd文件

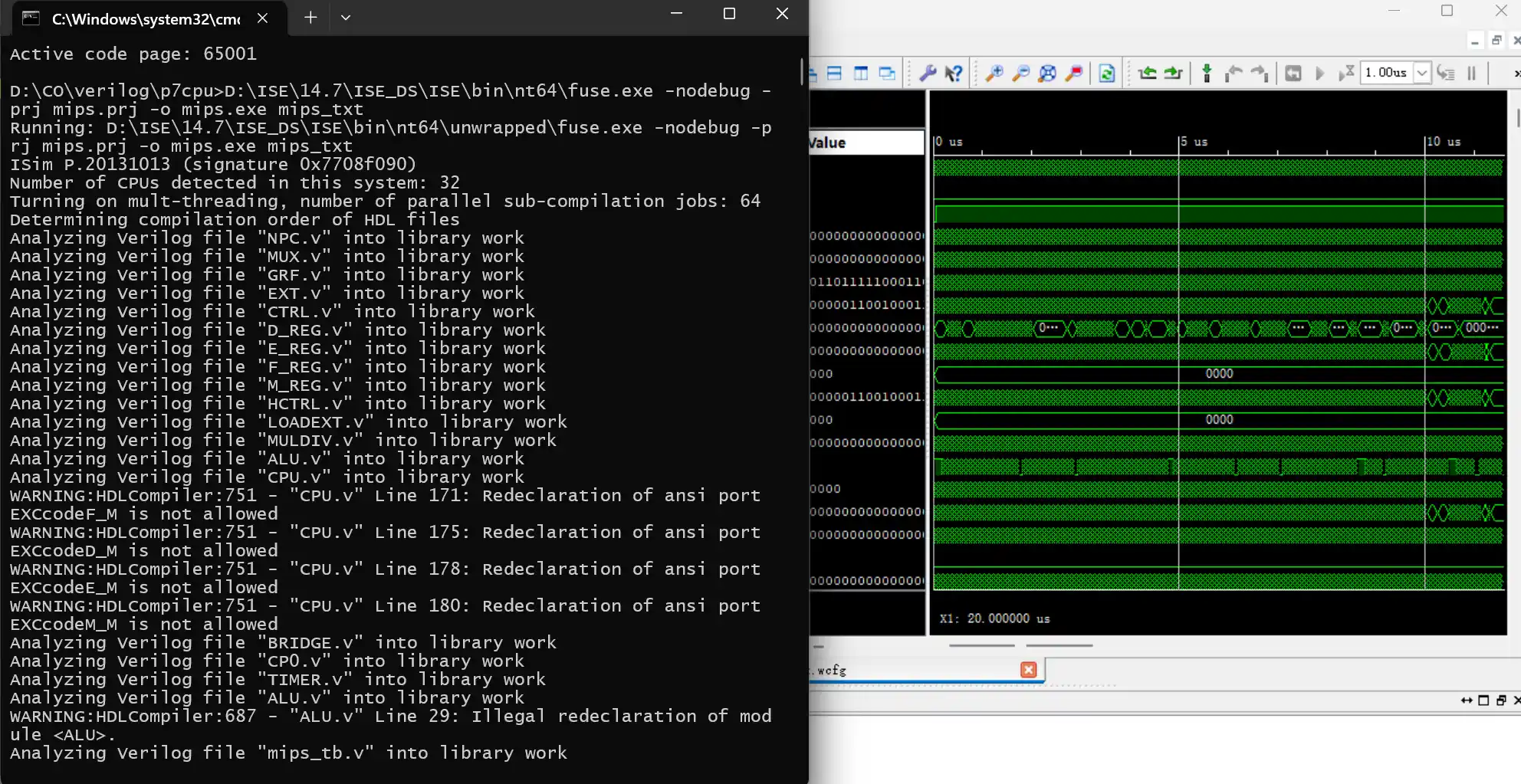

二.课上通过命令行调用 ISE 工具链

由于机房环境没有配置iverilog,因此无法使用其编译项目,也同样无法使用vvp和gtkwave进行仿真和波形查看,但是ISE能够运行仿真,其文件夹内部必然有相关仿真和波形查看的程序,理论上可以通过命令行调用。

使用命令行工具(如 fuse.exe 和 isimgui.exe)完成编译、仿真和波形查看。具体命令详见下文。

通过这种方式,你可以摆脱 ISE的 GUI 界面,专注于代码开发和仿真分析,虽然没有格式化和vscode内的语法报错,但是在编译时可以查看报错。

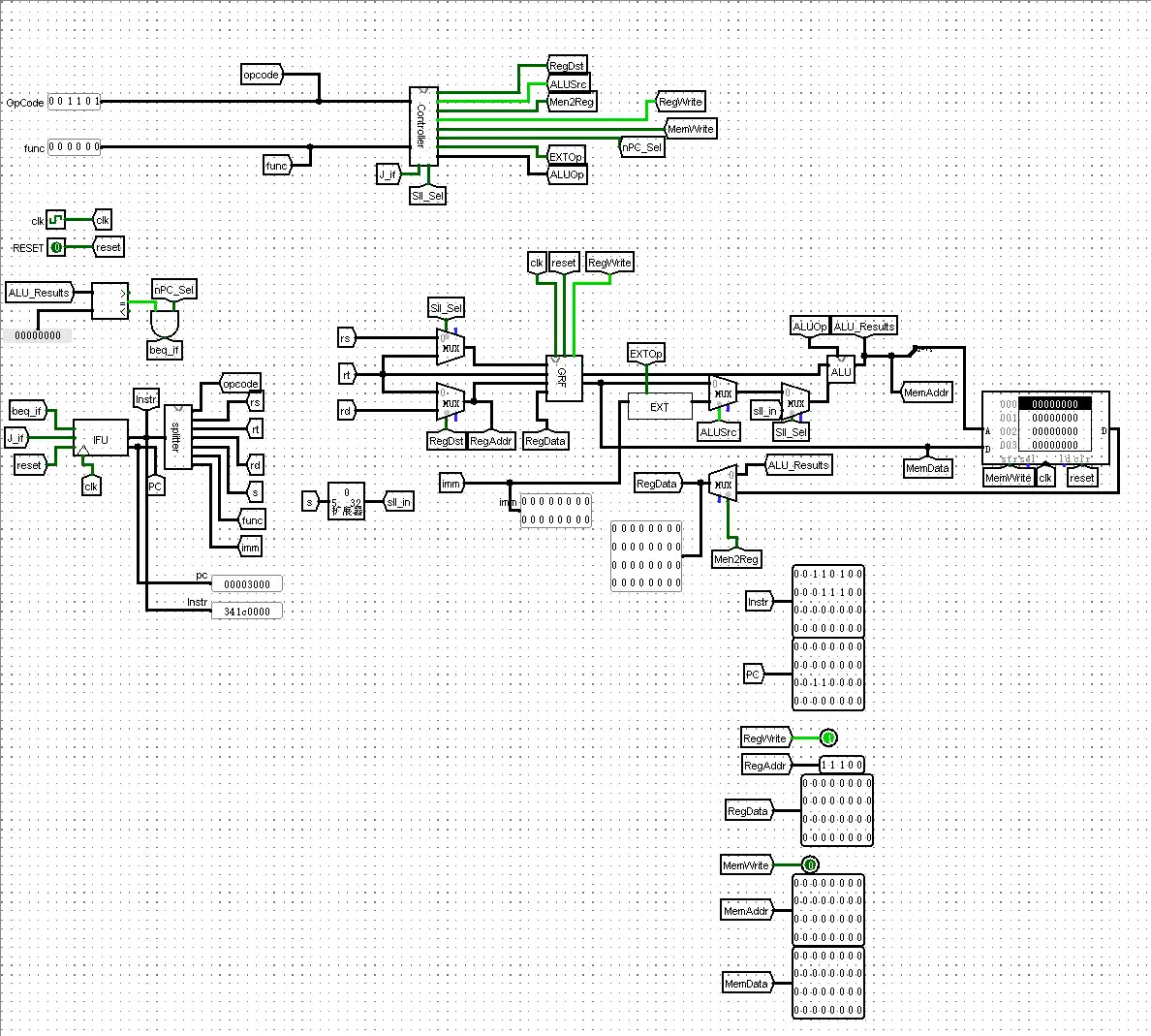

项目结构

运行前的项目结构如下:

1 | project/ |

mips.tcl 示例

仿真配置:

1 | wave log -r uut |

mips.prj 示例

依赖文件声明:

1 | verilog work "a.v" |

运行仿真和查看波形

1. 生成 mips.exe

运行以下命令生成可执行文件:

1 | %XILINX%\bin\nt64\fuse.exe -nodebug -prj mips.prj -o mips.exe mips_tb |

%XILINX%\bin\nt64\fuse.exe为你电脑上fuse.exe的路径,%XILINX%为预先配置的ISE环境变量,可以不配置而使用全路径。

如上成功后,项目目录中会新增以下文件:

1 | project/ |

2. 运行仿真

执行以下命令运行仿真:

1 | mips.exe -nolog -tclbatch mips.tcl |

运行后,命令行窗口会显示输出内容(如果 testbench 文件有输出)。

项目目录中会新增波形文件 isim.wdb:

1 | project/ |

3. 查看波形

运行以下命令查看波形:

1 | %XILINX%\bin\nt64\isimgui.exe -view isim.wdb |

至此,成功在外部命令行运行仿真并查看波形。

上机前将相关命令记录在 txt 文件中,和 tcl、prj 文件一并提交,即可在上机开箱即用。

三.课下其他配置

因为课上无法联网和配置其他环境,因此课上使用第二章节的配置,课下可以使用其他的环境。

未经过助教认证的内容

如果询问允许上传iverilog到课上环境,可以使用以下的环境配置。

1. 生成 mips.exe

在testbench中加入以下块:

1 | initial |

**注意mips_txt**为tb模块名称,而不是tb文件名称

读入所有.v文件编译程序

1 | iverilog -o mips -y ./ *.v |

2. 运行仿真

调用vvp运行仿真并且生成波形图

1 | vvp -n mips -lxt2 |

3. 查看波形

调用gtkwave查看波形

1 | gtkwave mips.vcd |

注意事项

- 提交文件:上机前将相关命令记录在

txt文件中,和tcl、prj文件一并提交。 - 问题排查:若出现问题,可删除除初始文件外的所有文件并重新生成。每次修改后需重新生成。

- 波形图限制:波形图只能打开一个。若

isim图形化界面报错,检查是否有未关闭的波形图窗口。 - 批处理文件问题:编写

bat文件一次性运行三条指令可能会出现未知问题,建议逐条执行。