BUAA-OS-LAB2

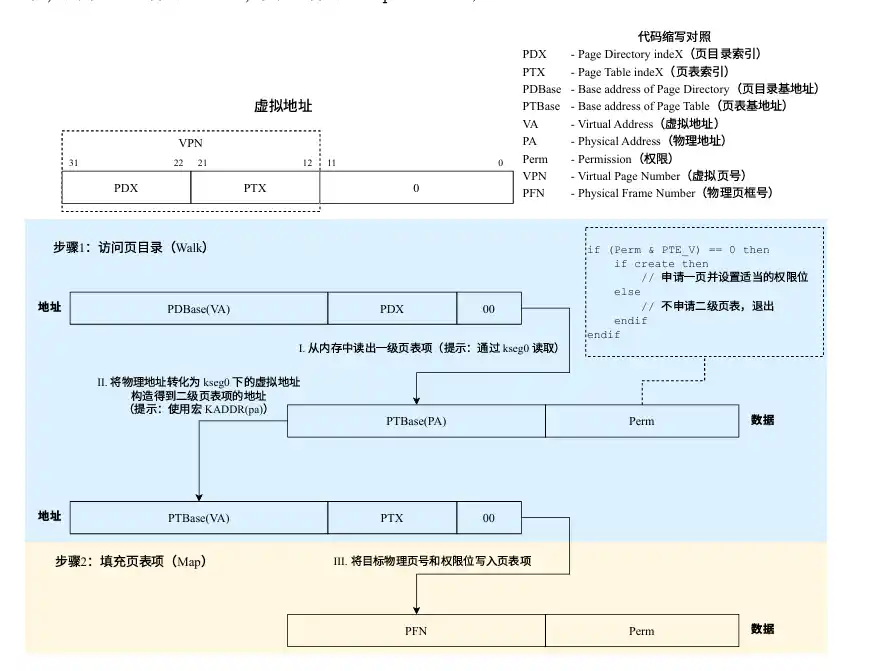

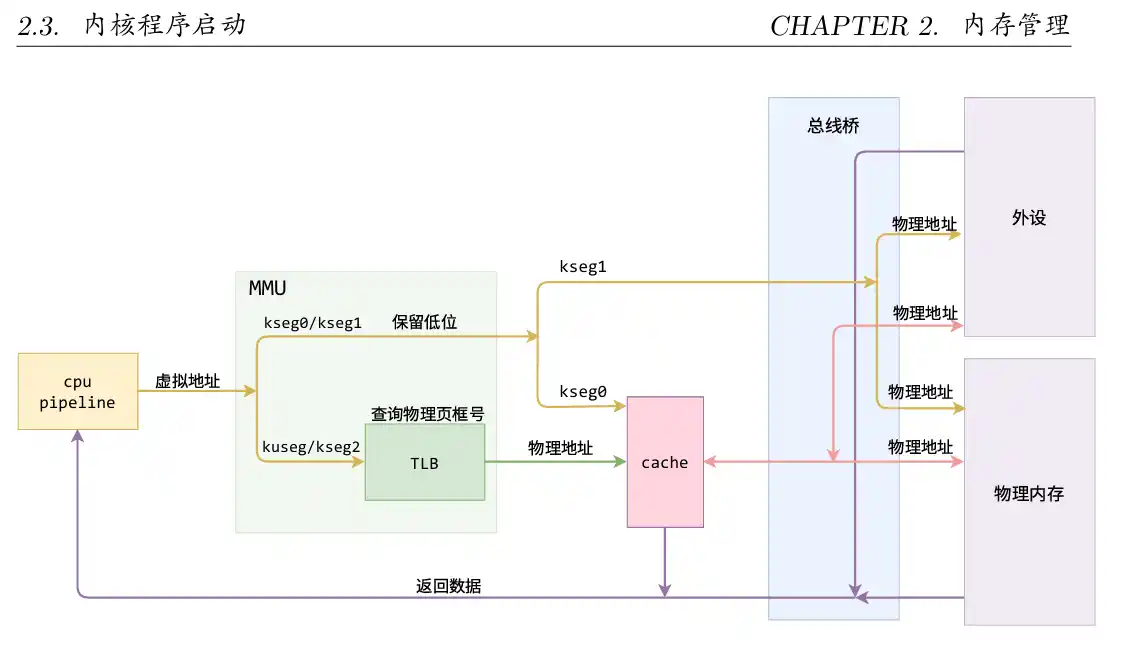

BUAA OS LAB2 实验报告ThinkingThinking 2.1Q:

请根据上述说明,回答问题:在编写的 C 程序中,指针变量中存储的地址 被视为虚拟地址,还是物理地址?MIPS 汇编程序中 lw和sw 指令使用的地址被视为虚 拟地址,还是物理地址?

A:

实际程序中,访存、跳转等指令以及用于取指的PC寄存器中的访存目标地址都是虚拟地址。我们编写的C程序中中指针的值也是虚拟地址。

Thinking 2.2Q:

•从可重用性的角度,阐述用宏来实现链表的好处。

•查看实验环境中的/usr/include/sys/queue.h,了解其中单向链表与循环链表的实 现,比较它们与本实验中使用的双向链表,分析三者在插入与删除操作上的性能差 异。

A:

宏的的特性就是可重复使用。当这段代码的具体实现需要更改时,只需要改宏这一处就行。宏相比函数由于是字符串的替换,因此不必进行地址的跳转和栈的保存。

在实验环境中,只看到了单向链表、双向链表、单向队列、双向队列、循环队列,感觉循环队列在插入和删除操作方面和循环链表没太大差异,据此进一步分析。

插入操作:单向链表插入操作十分简单,两行代 ...

BUAA-OS-LAB1

BUAA OS LAB1 实验报告ThinkingThinking 1.1Q:

在阅读附录中的编译链接详解以及本章内容后,尝试分别使用实验环境中 的原生 x86 工具链(gcc、ld、readelf、objdump 等)和 MIPS 交叉编译工具链(带有 mips-linux-gnu- 前缀,如 mips-linux-gnu-gcc、mips-linux-gnu-ld),重复其中的编 译和解析过程,观察相应的结果,并解释其中向objdump传入的参数的含义。

A:

编写程序hello.c

123456#include <stdio.h>int main(){ printf("Hello World!\n"); return 0;}

这里只截取.text部分

x86 .o

123456789101112131415am.o: 文件格式 elf64-x86-64Disassembly of section .text:0000000000000000 <main>: 0: f3 0f 1e ...

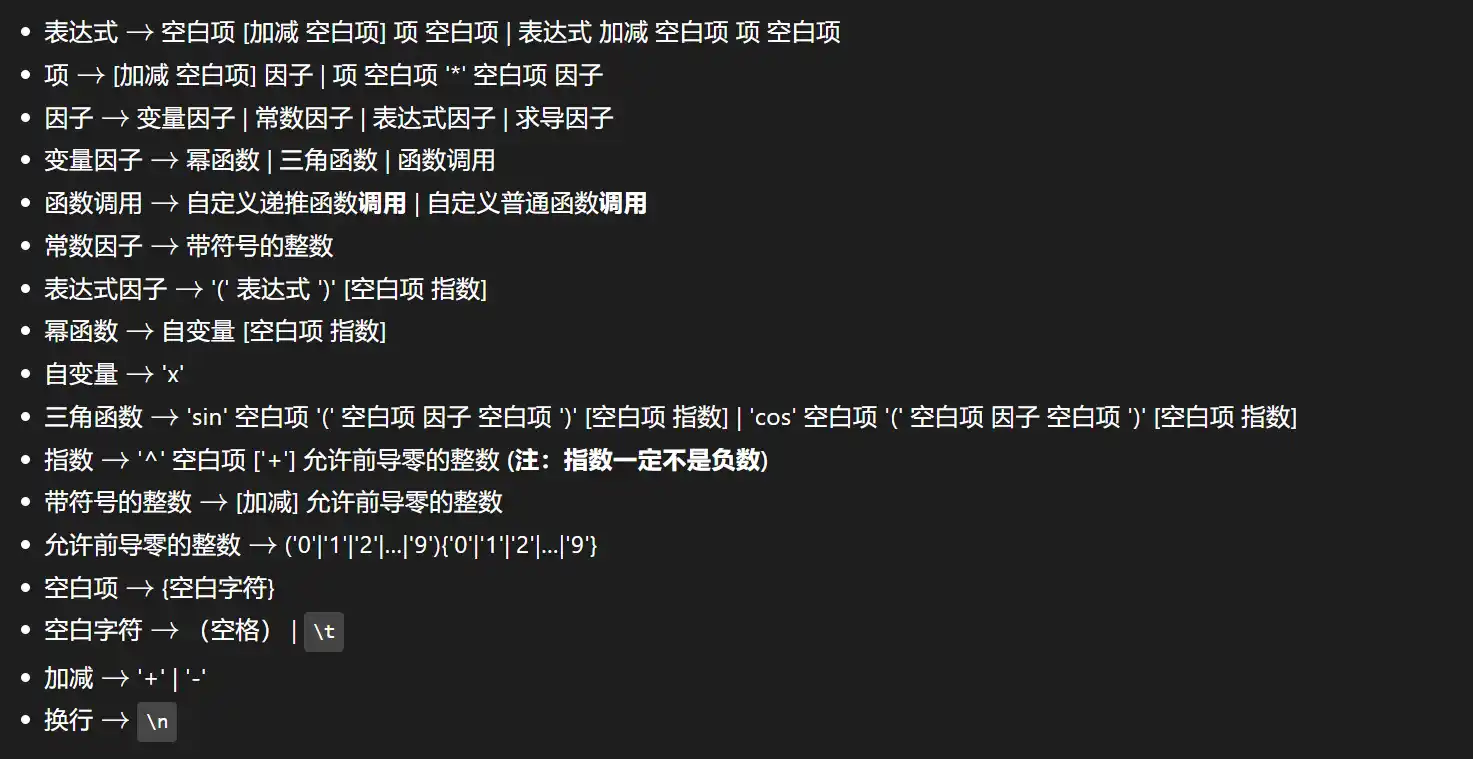

BUAA-OO-unit1

OO Unit1 Summary基于度量的代码分析与迭代过程

注:

CogC是认知复杂度,衡量代码的难以理解的程度,CogC说明代码比较难以理解。

ev(G)是基本复杂度,衡量非结构化程度,ev(G)高意味着难以模块化和维护。

iv(G)是模块设计复杂度,衡量模块的调用关系,iv(G)高意味着模块之间的耦合性高,难以隔离和复用。

v(G)是圈复杂度,衡量结构的复杂程度,v(G)是说明代码难以测试和维护。

hw1重点思路及迭代过程:

修改项的定义,实现将表达式分为不剩下符号的一个个项

term ——>[+-]{0,2} factor 修改定义实现多余符号匹配

项符号去多余判断符号,累加

因子,累乘,最后结果符号设置为项

原子组和慵懒防止递归爆炸

递归处理表达式因子,正则每次匹配内层,但是有特殊情况如下

((x-1))*((x-1)),判断匹配结果表达式后有*取消计算,防止错误匹配的表达式因子

类图:

PatternString类存储所有需要使用的正则表达式,防止重复声明,Simplify为顶层化简函数,内含有化简表达式、化简项、化简因子的方法逐层递归 ...

BUAA-OS-LAB0

BUAA OS LAB0 实验报告ThinkingThinking 0.1Q:

• 在前述已初始化的~/learnGit 目录下,创建一个名为 README.txt 的文件。执 行命令git status > Untracked.txt(其中的 > 为输出重定向,我们将在 0.6.3 中 详细介绍)。• 在README.txt 文件中添加任意文件内容,然后使用 add 命令,再执行命令 git status > Stage.txt。 • 提交README.txt,并在提交说明里写入自己的学号。• 执行命令cat Untracked.txt 和 cat Stage.txt,对比两次运行的结果,体会 README.txt 两次所处位置的不同。• 修改README.txt 文件,再执行命令git status > Modified.txt。• 执行命令cat Modified.txt,观察其结果和第一次执行 add 命令之前的 status 是 否一样,并思考原因。

A:

分别处于未追踪,待提交

commit后处于已提交的状态,status里不可见

修改后处于 ...

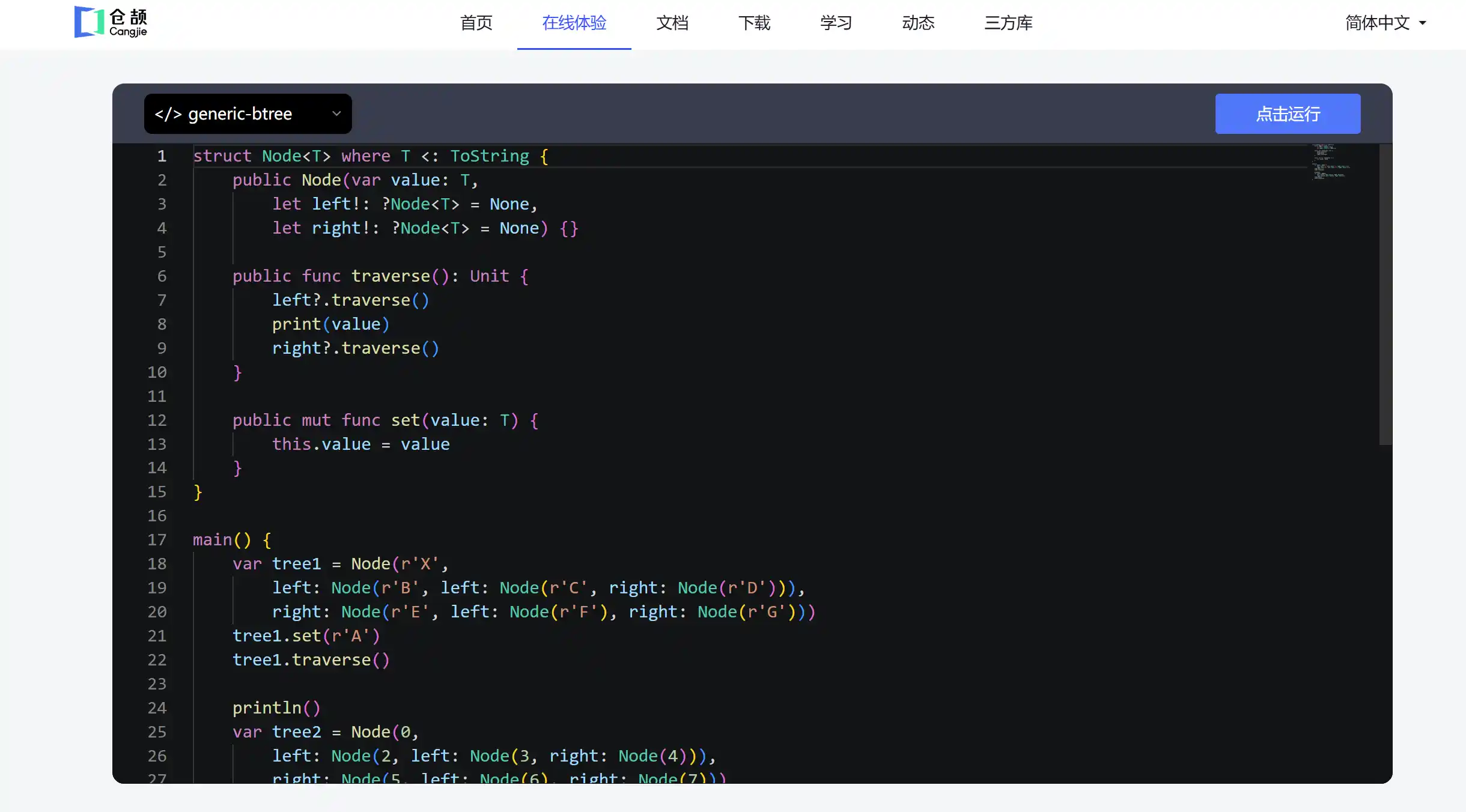

仓颉语言+vscode配置

仓颉语言+vscode配置1.仓颉简介仓颉编程语言是一种面向全场景应用开发的通用编程语言,可以兼顾开发效率和运行性能,并提供良好的编程体验,主要具有如下特点:

语法简明高效:仓颉编程语言提供了一系列简明高效的语法,旨在减少冗余书写、提升开发效率,例如插值字符串、主构造函数、Flow 表达式、match、if-let、while-let 和重导出等语法,让开发者可以用较少编码表达相关逻辑。

多范式编程:仓颉编程语言支持函数式、命令式和面向对象等多范式编程,融合了高阶函数、代数数据类型、模式匹配、泛型等函数式语言的先进特性,还有封装、接口、继承、子类型多态等支持模块化开发的面向对象语言特性,以及值类型、全局函数等简洁高效的命令式语言特性。开发者可以根据开发偏好或应用场景,选用不同的编程范式。

类型安全:仓颉编程语言是静态强类型语言,通过编译时类型检查尽早识别程序错误,降低运行时风险,也便于代码维护。同时,仓颉编译器提供了强大的类型推断能力,可以减少类型标注工作,提高开发效率。

内存安全:仓颉编程语言支持自动内存管理,并在运行时进行数组下标越界检查、溢出检查等,确保运行时内存安全。

高效并 ...

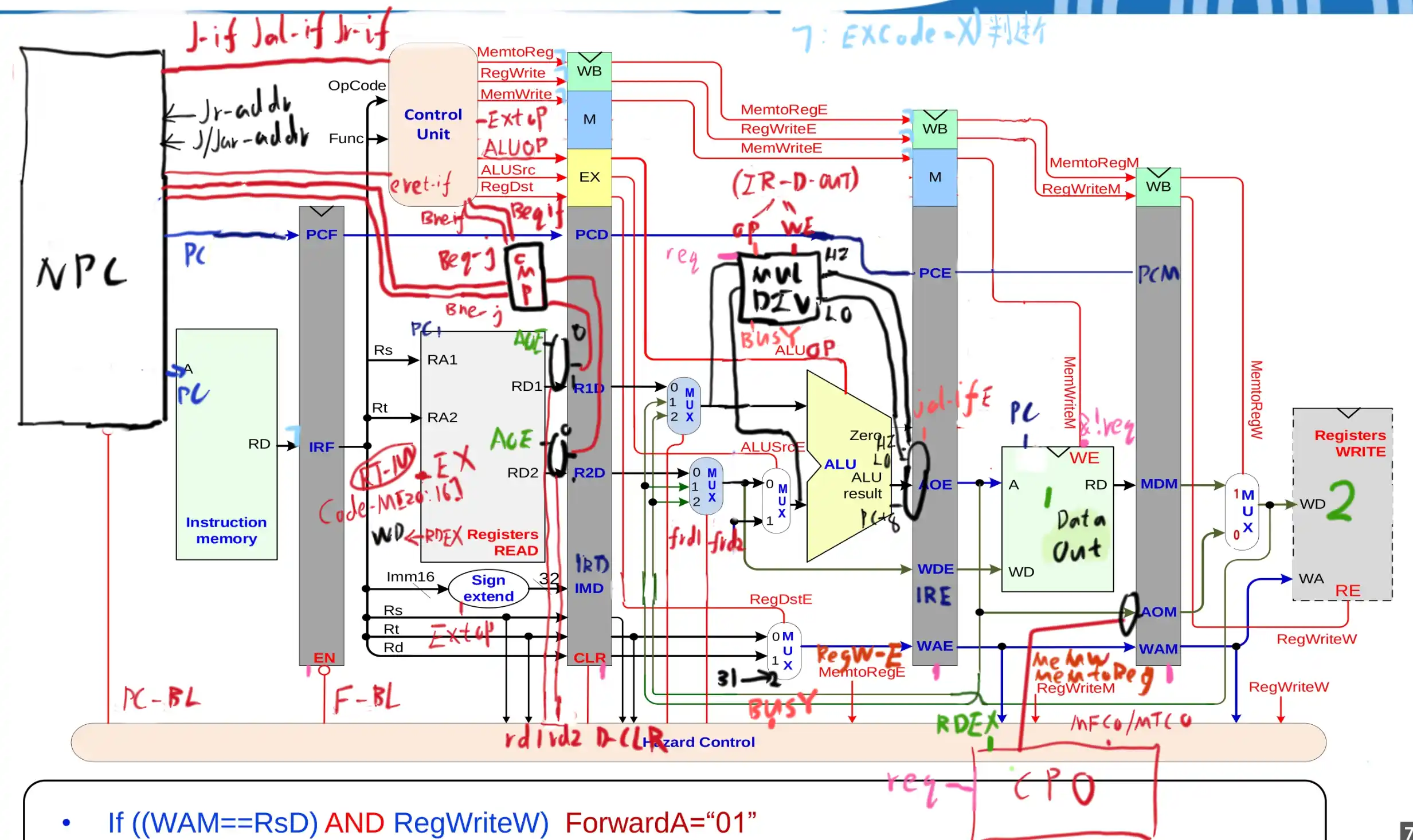

BUAA-CO-P7-verilog五层流水线CPU(全指令)

verilog五层流水线CPU-P7(全指令+异常中断处理+外设连接)模块设计整体视图:

cpu:

1. GRF(寄存器堆)

端口名

输入\输出

位宽

功能

clk

Input

1

时钟信号

reset

Input

1

复位信号

WE

Input

1

使能信号

PC

Input

31:0

pc

A1

Input

4:0

输入寄存器地址端口1

A2

Input

4:0

输入寄存器地址端口2

A3

Input

4:0

输入寄存器地址端口3,写寄存器地址

EXTRA

Input

4:0

输入寄存器地址端口EX,读寄存器地址

WD

Input

31:0

数据输入端口,输入一个32位数据,存入编码为A3的寄存器中

RD1

Output

31:0

输出编码为A1中输入的寄存器中的值

RD2

Output

31:0

输出编码为A2中输入的寄存器中的值

RDEXTRA

Output

31:0

输出编码为EXTRA中输入的寄存器中的值

初始化!!

12345678910111213141516171819202122232425262 ...

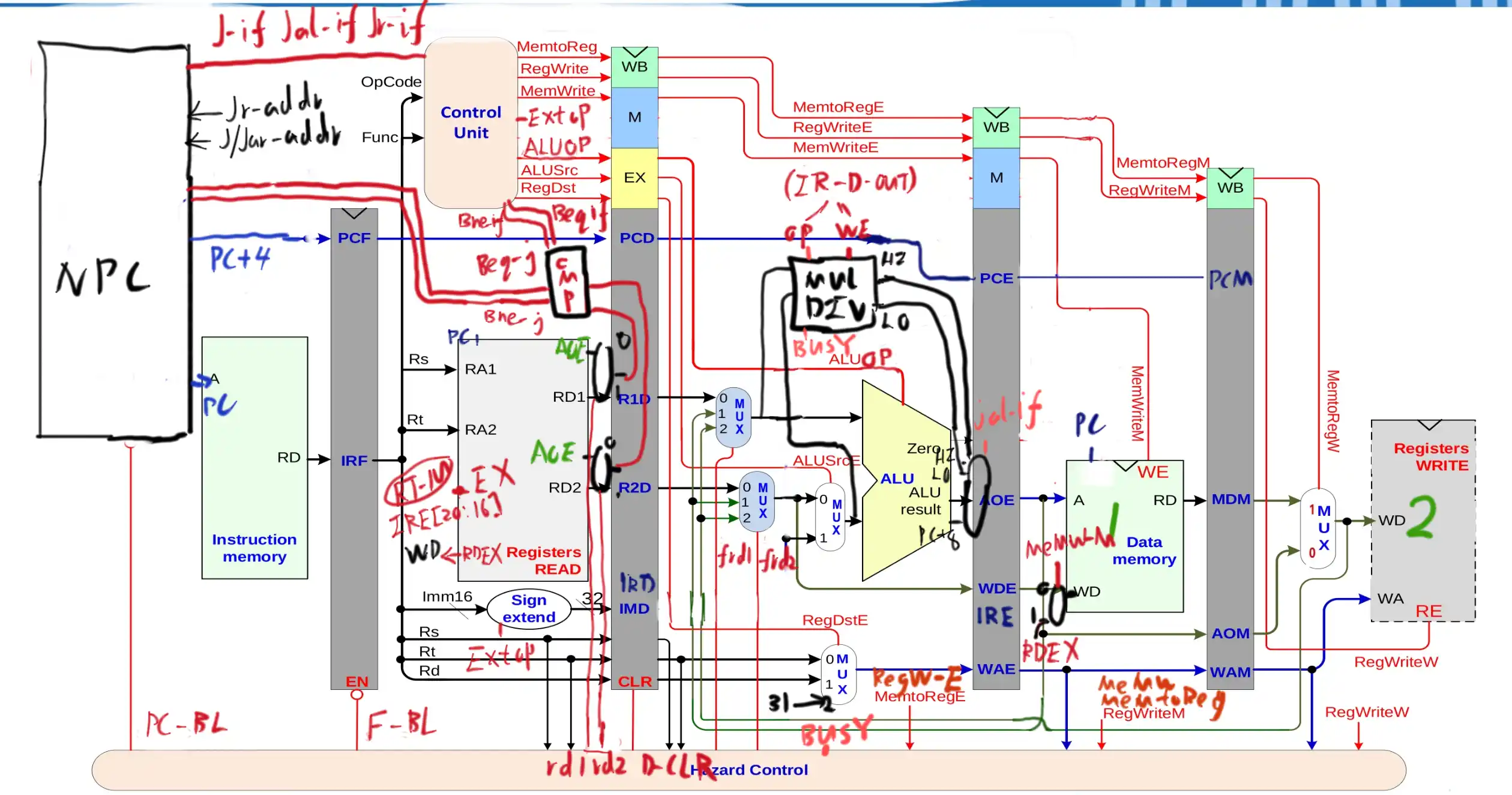

BUAA-CO-P6-verilog五层流水线CPU(全指令)

P6-verilog五层流水线CPU(全指令)模块设计整体视图:

1. GRF(寄存器堆)

端口名

输入\输出

位宽

功能

clk

Input

1

时钟信号

reset

Input

1

复位信号

WE

Input

1

使能信号

PC

Input

31:0

pc

A1

Input

4:0

输入寄存器地址端口1

A2

Input

4:0

输入寄存器地址端口2

A3

Input

4:0

输入寄存器地址端口3,写寄存器地址

EXTRA

Input

4:0

输入寄存器地址端口EX,读寄存器地址

WD

Input

31:0

数据输入端口,输入一个32位数据,存入编码为A3的寄存器中

RD1

Output

31:0

输出编码为A1中输入的寄存器中的值

RD2

Output

31:0

输出编码为A2中输入的寄存器中的值

RDEXTRA

Output

31:0

输出编码为EXTRA中输入的寄存器中的值

初始化!!

12345678910111213141516171819202122232425262728293031323334353 ...

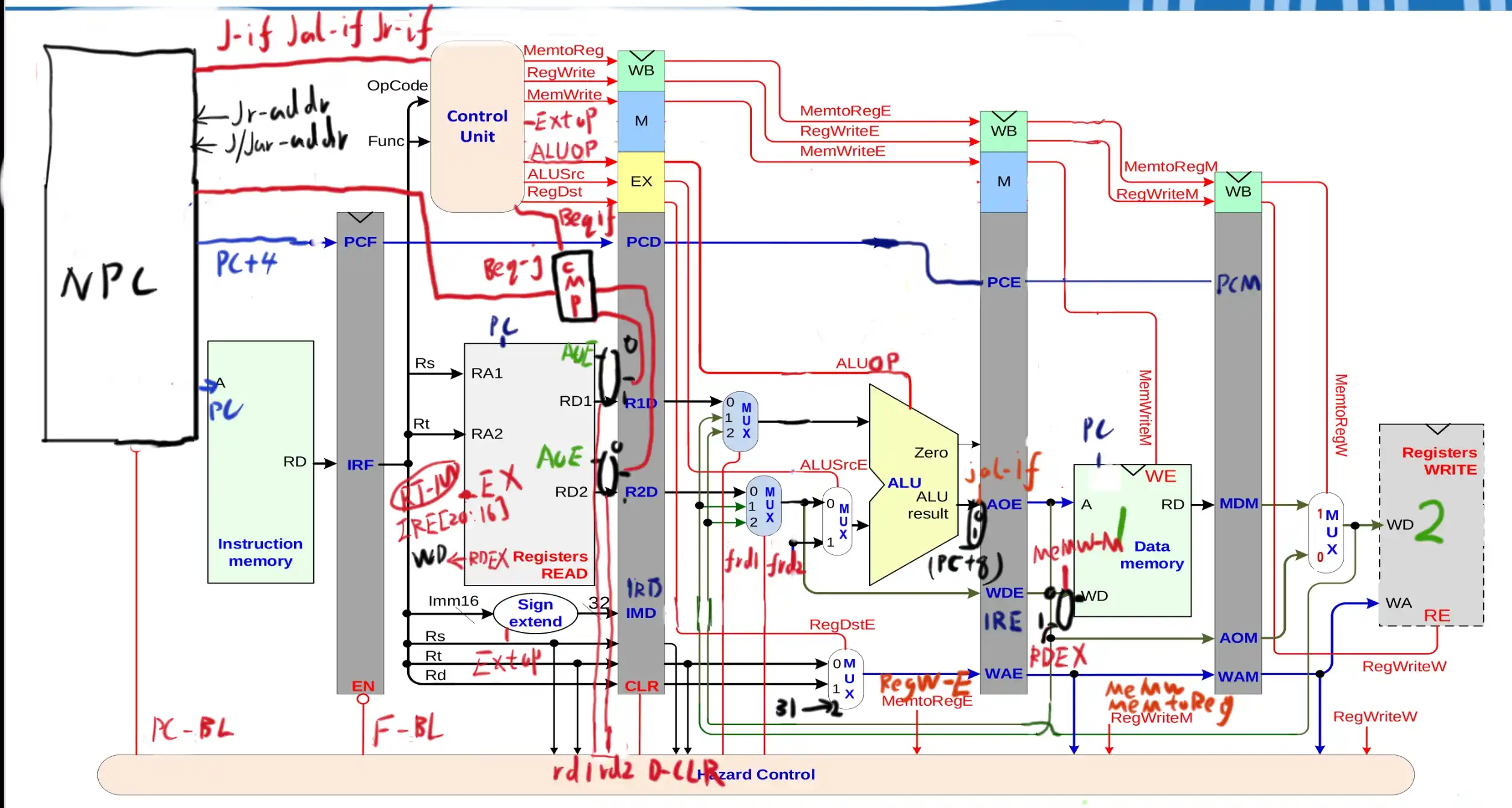

BUAA-CO-P5-verilog五层流水线CPU(简化指令)

verilog五层流水线CPU(简化指令)模块设计整体视图:

1. GRF(寄存器堆)

端口名

输入\输出

位宽

功能

clk

Input

1

时钟信号

reset

Input

1

复位信号

WE

Input

1

使能信号

PC

Input

31:0

pc

A1

Input

4:0

输入寄存器地址端口1

A2

Input

4:0

输入寄存器地址端口2

A3

Input

4:0

输入寄存器地址端口3,写寄存器地址

EXTRA

Input

4:0

输入寄存器地址端口EX,读寄存器地址

WD

Input

31:0

数据输入端口,输入一个32位数据,存入编码为A3的寄存器中

RD1

Output

31:0

输出编码为A1中输入的寄存器中的值

RD2

Output

31:0

输出编码为A2中输入的寄存器中的值

RDEXTRA

Output

31:0

输出编码为EXTRA中输入的寄存器中的值

初始化!!

1234567891011121314151617181920212223242526272829303132333435363 ...

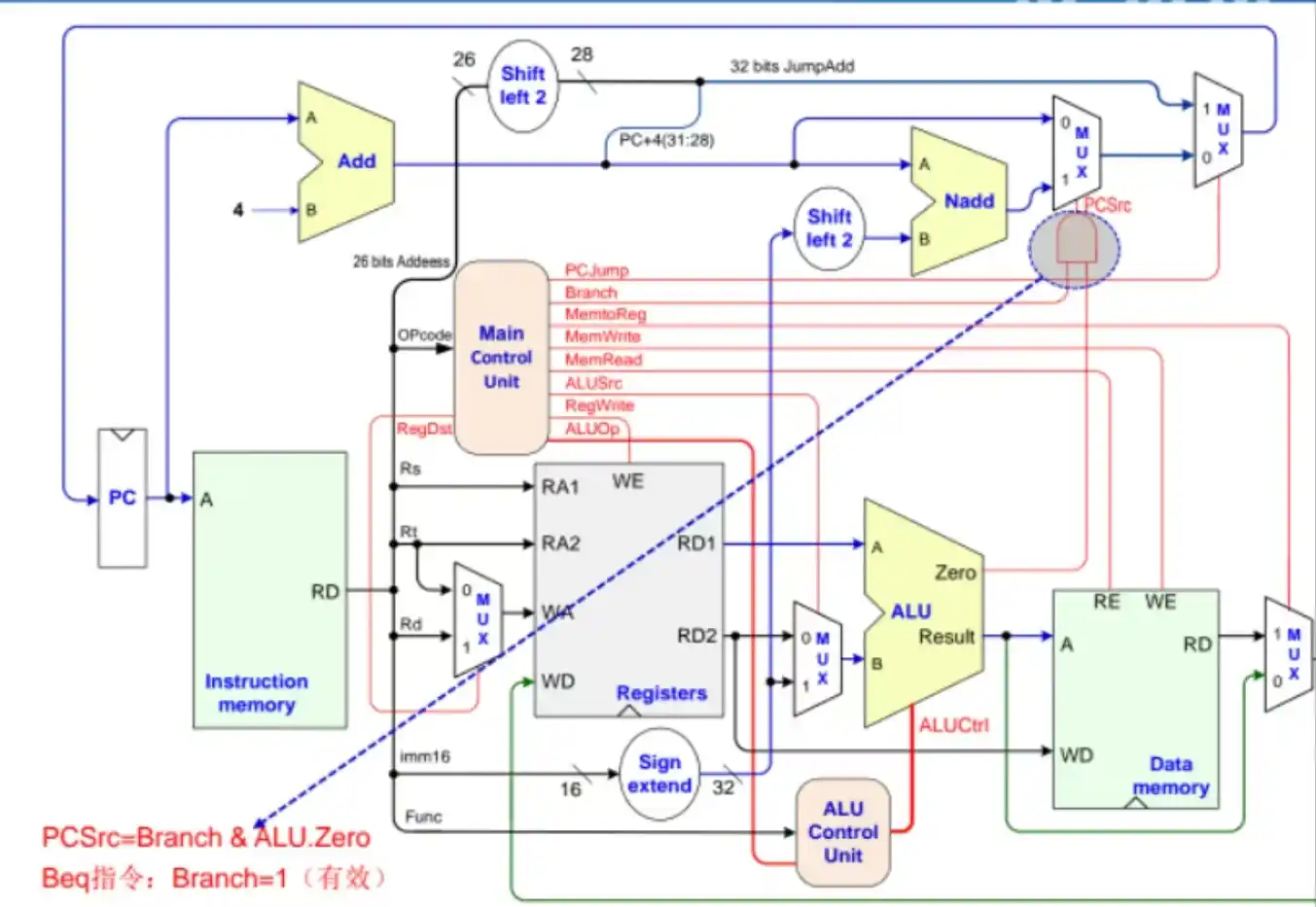

BUAA-CO-P4-verilog单周期CPU(简化指令)

verilog单周期CPU(简化指令)模块设计整体视图:

1. GRF(寄存器堆)

端口名

输入\输出

位宽

功能

clk

Input

1

时钟信号

reset

Input

1

复位信号

WE

Input

1

使能信号

PC

Input

31:0

pc

A1

Input

4:0

输入寄存器地址端口1

A2

Input

4:0

输入寄存器地址端口2

A3

Input

4:0

输入寄存器地址端口3,写寄存器地址

WD

Input

31:0

数据输入端口,输入一个32位数据,存入编码为A3的寄存器中

RD1

Output

31:0

输出编码为A1中输入的寄存器中的值

RD2

Output

31:0

输出编码为A2中输入的寄存器中的值

初始化!!

123456789101112131415161718192021222324252627282930313233343536373839module GRF( input clk, input reset, input WE, input [31:0] PC, input [4 ...

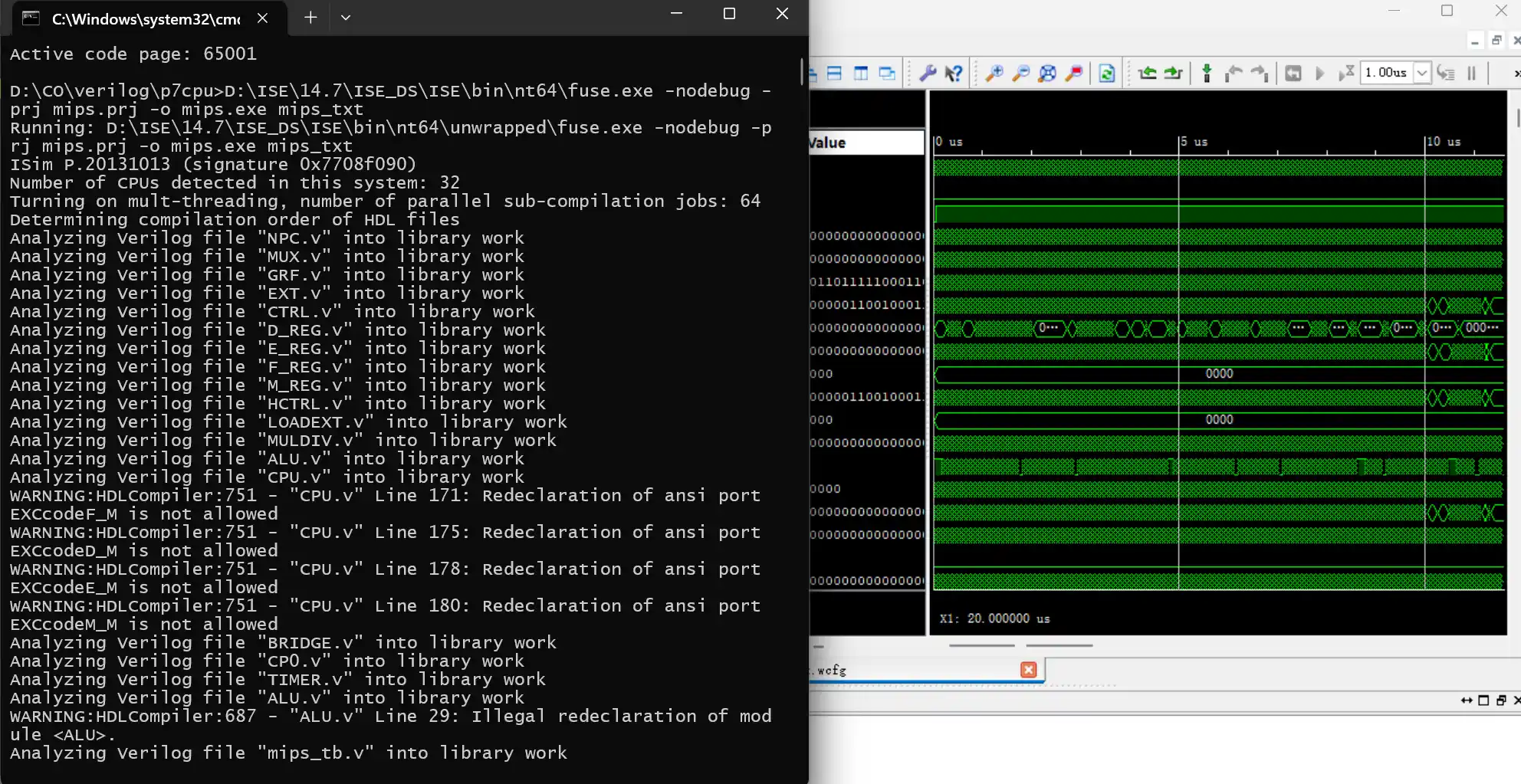

BUAA-CO-ISE外部运行配置

ISE 外部运行配置为了避免使用 ISE 自带的界面(其 GUI 界面较为陈旧且运行速度较慢),我们可以选择通过现代化编辑器(如 VS Code)编写 .v 文件,并结合 ISE 的核心工具完成仿真运行。

这种方法不仅提升了开发效率,还能利用 VS Code 的强大功能(如代码高亮、自动补全、版本控制等)优化开发体验。以下是具体的实现步骤和注意事项:

一. 使用 VS Code 编写 Verilog 文件在项目目录中创建或编辑 .v 文件,确保代码结构清晰、模块划分合理。推荐安装 Verilog HDL 插件以提升编写和调试效率。

vscode插件配置所有所需下载懒人链接:点击下载

代码格式化正如上面整体思路中所写,需要在 VSCode 中装一个插件:

然后从 Github 仓库中下载 verible-verilog 工具win64版本:https://github.com/chipsalliance/verible/releases

Windows 直接解压到合适的位置,并复制其中 verible-verilog-format.exe 的地址,填入 VSCode 的设置中:

注意 ...